I have been working with Eagle for quite some time but never really got a PCB manufactured. almost all the time i used the toner transfer method to make homebrew PCBs. But then i took a project in which i had to use SMD components and i could no longer use toner transfer method because of the limits on resolution of the Laser printer.

Time had come for “properly” designing and generating “Gerber files”. When you are using toner transfer then there isn’t really a need to go into minute details of every layer as you know what you want exactly, but this approach dosen’t work with the manufacturers. Hence you have to take a lot of precautions and understand what exactly you are doing.

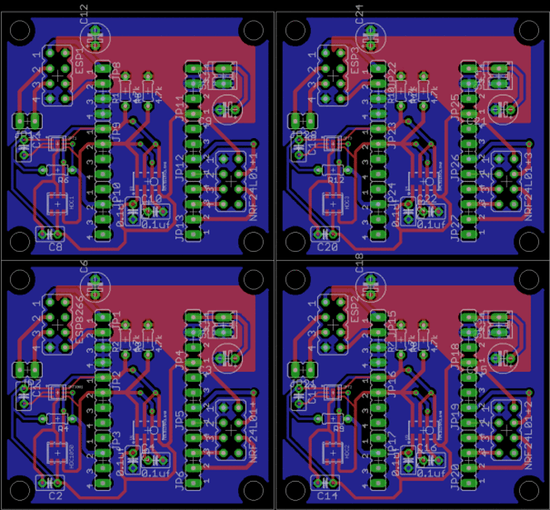

Till designing is okay for most of us. But then i needed to “Panelize” and then create the “Gerber” files.

PANELIZE

This is fairly easy to do. Just save your .brd and .sch files after you are done with the design. After that in the same folder create a new .brd file by doing File -> Your Project -> New -> Board

Now just save this board file without adding anything to it and name it as “project_name_panel.brd”. After that open your project and select the whole board then click on the “copy” icon. After that browse to your panel board file and then click on “Paste” icon. The whole board would be copied. Similarly you can copy “Different” board files(from different projects) into a SINGLE panel board file.

This step is NOT yet complete. Because of what you did just now Eagle will rename the component name so that no two components have the same name. So even if you are not copying a different board but making multiple copies of a single board the names of the components will be changed.

This step is NOT yet complete. Because of what you did just now Eagle will rename the component name so that no two components have the same name. So even if you are not copying a different board but making multiple copies of a single board the names of the components will be changed.

Notice the capacitor on the top in all the boards. They all have different names although they are the same.

Why ? Once the copy is placed on the board, Eagle automatically changes the part names to avoid duplication. Normally this is not a problem, but when you want to panelize a design you want all the panels to come out exactly the same. Some of you might be fine with this but some of you might not be. This especially becomes a nuisance if the board is of moderate to high complexity and has a lot of components. For that we run the “panelize.ulp” ULP. There are two ways to do that –

For more detail: Panelizing and Gerber Generation in Eagle