Altera is providing programming support for its ARM-based SoCs using industry-standard workflows from MathWorks.

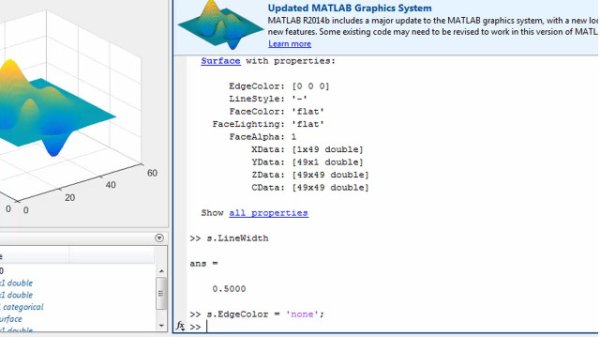

Release 2014b from MathWorks includes an automated, model-based design workflow optimised for Altera SoCs.

Designers using this flow can accelerate their algorithmic designs in Altera SoCs while staying in a high-level programming environment and save weeks of development time.

“Today’s announcement is a significant extension to our partnership with Altera, enabling our customers to quickly and easily leverage the performance and system-level benefits that Altera SoCs provide,” says MathWorks’ Ken Karnofsky, “engineers now have a highly-automated SoC workflow for modeling algorithms in MATLAB and Simulink, simulating with system test benches, partitioning into hardware and software subsystems, generating C and HDL code, and prototyping with Altera design tools and development kits.”

The integrated hardware/software workflow allows programmers to simulate, prototype, verify and implement algorithms that target both the FPGA and ARM processors integrated in Altera SoC FPGAs.

The design flow automatically generates the interfaces between the FPGA, the processor system and the software drivers. Targeted support for Altera SoCs is included in two MathWorks code generation products, the HDL Coder and Embedded Coder tools.

Using a single development environment, engineers use HDL Coder to generate custom IP cores and configure the programmable logic portion of the SoC, while Embedded Coder is used to generate C/C++ code that runs on the ARM-based hard processor system.

A model-based design environment targeting Altera SoCs accelerates the design process by allowing designers to stay in a familiar design environment without requiring designers to be experienced hardware engineers.

For more detail: MathWorks helps programme Altera SOCs