Cortus, which licenses small 32-bit cores, has upgraded its instruction set and launched two new cores which use the new one.

Why upgrade? “Embedded applications have got more complex,” replies Cortus vice-president Roddy Urquhart.

The new V2 instruction set is 50% bigger than its V1 predecessor and the instruction memory uses about 20% less power, according to Cortus.

APS23 is the first processor core with the V2 instruction set and is aimed at low power always on/always listening systems and those with less demanding clock frequencies such as Bluetooth Smart.

“We have focused on reducing the size of the instruction memory which is usually the largest single component in a system and are seeing an average 16% improvement in code density over our earlier (V1) cores,” says Cortus CEO Michael Chapman.

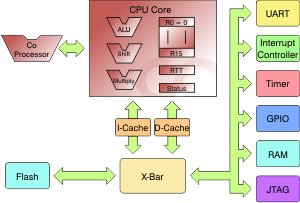

The APS23 has a Harvard architecture, 16 32-bit registers, a three-stage pipeline and a sequential multiplier. It supports the AXI4-Lite bus as well as Cortus APS peripherals. The core delivers 2.83DMIPS/MHz and 1.44CoreMarks/MHz in computational performance. The minimal usable APS23 CPU starts around 9.8kgates when optimised for area. Dynamic power is 12µW/MHz with a 90nm process (Cortus cores are synthesisable and foundry independent).

The Cortus v2 instruction set allows the seamless mixing of 16-bit, 24-bit and 32-bit instructions without mode switching. This instruction set is richer than the v1 instruction set which used a mix of 16-bit and 32-bit instructions.

Cortus will continue to offer products based on the v1 instruction set (APS3R) in parallel with the new cores based on the v2 instruction set. All C/C++ or assembler code developed for the v1 cores can be used unmodified on the v2 cores.

All cores interface to Cortus’ peripherals including Ethernet 10/100 MAC, USB 2.0 Device and USB 2.0 OTG via the efficient APS bus. They also share the simple vectored interrupt structure, which ensures rapid, real time interrupt response, with low software overhead.

The APS tool chain and IDE (for C and C++) is available to licensees free of charge, and can be customised and branded for final customer use. Ports of various RTOSs are available such as FreeRTOS, Micrium μC/OSII.

The second Cortus core with the V2 instruction set is the APS25 aimed at embedded systems demanding greater computational performance and system complexity while also requiring maximum code density and extendibility..

For more detail: Cortus upgrades instruction set, launches two new cores